最新のPCの内部では、PCI ExpressやSerial ATAのように「ギガビット伝送」と呼ばれる非常に高速なシリアル信号伝送方式が使われている。実は、それらより低速な信号を使うメモリーバスの方がシステムを設計する上で難しい。理由は大きく2つ。1つは、メモリーバスがパラレル(並列)バスである点。もう1つは信号の接続先が複数あり、なおかつモジュールという取り外しを前提とした実装方式になっている点だ。

高速シリアルバスには及ばないものの、メモリーバスは、DDR2-800でデータ信号線1本当たり800Mビット/秒であり、十分に速い。これはかつてDirect RDRAMが実現していた速さで、当時のマザーボードは厳しい条件を守って設計されていた。Direct RDRAMは16ビット幅でパケットベースのデータを伝送するシリアルライクなバスであったが、DDR2は驚くべきことに、パラレルバスで実現している。

パラレルバスのボード設計を難しくしている最も大きな要因は、各信号線を伝わるビット情報が受信側のデバイスで同時に受け取られなければならない、という条件だ。DDR2メモリーモジュールの場合、64本もあるデータ信号のタイミングをそろえる必要がある。DDR2-800のデータ信号はパルス幅が1.25ナノ秒あり、そのうち最大0.5ナノ秒がデバイスが受信する際に要求されるので、残るわずか0.75ナノ秒を、タイミングずれやノイズ、信号波形のゆがみなどの吸収で分け合う必要がある。

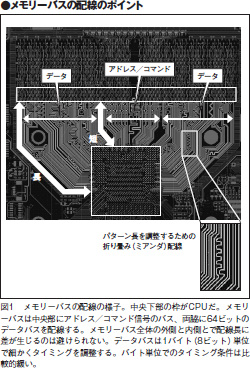

物理的にメモリーバスは、一辺約4cm幅のCPUから幅約12cmのメモリーソケットまで扇状に広がるように配線することになる。当然、中央部と端では配線の長さに大きな差が生じる(図1)。マザーボード上のパターンを観察すると、折り畳み配線されていることに気付くだろう。このような「等長配線」や「等遅延配線」と呼ばれるテクニックを使って、ボード設計でタイミングを合わせる努力がなされている。