|

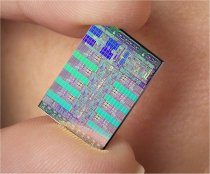

米IBM社,ソニー,ソニー・コンピュータエンタテインメント,東芝の4社が共同で開発を進めている次世代プロセッサ「Cell」(開発コード名)の全貌が明らかになった。2005年2月6日に始まった半導体の国際会議「ISSCC 2005(International Solid-State Circuits Conference)」で,4社はCellの試作チップの詳細仕様を初めて発表した。

今回明らかにした仕様は,最高動作周波数は4GHz超,プロセッサコア数は9で,内蔵メモリーは2Mバイト,など。メモリーバスと入出力インタフェースの帯域,プロセッサコアの数でパソコン向けマイクロプロセッサを引き離している。動作周波数は「一品モノ」に近い試作チップの値であるため一概には言えないが,トップクラスであることには違いない。

Cellが備えるプロセッサコアは2種類。64ビット・アーキテクチャのPowerシリーズをベースにしたプロセッサコア「Power Processor Element(PPE)」と,SIMD(Single Instruction/Multiple Data)命令の処理を担当する演算ユニット「Synergistic Processing Element(SPE)」である。前者を1個,後者を8個内蔵する。PPEは2スレッドを並列実行するSMT(Simultaneous Multithreading)機構を搭載。SPEの8スレッドを合わせると,Cell全体で最大10スレッドを並列実行できる。

Cellが備える九つのプロセッサコアは,互いに独立して動く。八つのSPEはそれぞれ256Kバイトのローカル・メモリーを持ち,個別のアドレス空間を備える。コア間でアドレス空間を共有しない。

外部メモリー用のインタフェースは,米Rambus社の「XDR」。12.8Gバイト/秒の帯域を持つ16ビット幅のチャネルを2本備える。計25.6Gバイト/秒の帯域がある。Pentium 4やAthlon 64の4倍だ。

グラフィックス・チップや他のCellとの接続に使う汎用の入出力インタフェースの帯域幅も広い。76.8Gバイト/秒の帯域を持つRambusの「FlexIO」インタフェースを備える。FlexIOインタフェースは最大2チャネルに分割して利用できる。例えば,ゲーム機として使うときはグラフィックス・チップと入出力チップ,サーバーとして使うときはCellを二つ接続,といった使い方ができる。

まだベールを脱いでいないのは,9コアを生かすOSだ。Cellを利用した製品計画は2005年1月に発表済み。IBMが2005年前半にエンジニアリング・サンプルの製造を開始。システムとしてはワークステーションを発売する。ソニーはホームサーバーとデジタル・ハイビジョン・テレビ(HDTV)を2006年内に製品化,など。しかしOSについては不透明だ。CellがOSやアプリケーションと組み合わせた形で姿を現すのは,今年5月に米国で開催されるアミューズメント機器の展示会「Electronics Entertainment Expo(E3)」にソニー・コンピュータエンタテインメントが展示する予定の次世代ゲーム機の試作機を待つことになりそうだ。

米IBM社

ソニー

ソニー・コンピュータエンタテインメント

東芝