論理設計を進めていくと,また難題が降りかかってきた。使用するトランジスタ数を2,000個以内にすることと,汎用レジスタやアドレススタックだけでなく,すべての論理にダイナミック回路の使用という要請であった。前回の訪問時に実施したトランジスタ数の見積もりでは,大きな容量を持つ信号線を駆動するドライバ回路,命令とシステムバスの制御などについて論理量の見積もりを行わなかった。したがって,要求された2,000個のトランジスタはかなりきついハードルと予想した。

さらに,レイアウト設計を行うマスク設計者が2人しかいないので,回路設計とレイアウト設計のプランとしても使えるように,4004CPUの論理設計をゲ-トレベルではなくトランジスタレベルで行う必要が生じた。

電卓の基板設計と同じく,その頃の半導体のレイアウトも2次元の世界だったので,電卓の基板設計の経験が生かされた。トランジスタという部品の配置を考え,横方向の配線にメタルを使い,縦方向の配線にポリシリコンや拡散層を使い,論理設計を行うことにした。PMOSトランジスタを使うために正論理ではなく負論理での論理設計となり,慣れるのに少々の時間がかかった。同時に,ダイナミック論理用の回路とレイアウトの勉強もしなければならなかった。

設計に入ると時間は待ってくれなかった。論理を如何に構築するかは重要だ。しかし,詳細な論理設計に入ると,論理の具体的な実装にあたっては,集中力を持続しつつ,自分の考え方を如何に収束させ最適化を図るかがより重要な課題となった。アーキテクチャ設計だけでなく,論理や回路設計においても最適化が重要な作業となった。

|

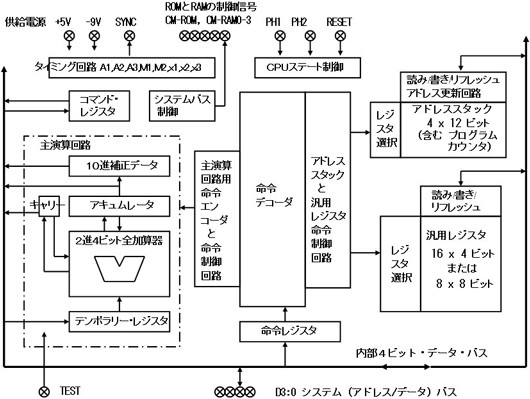

| 図1●4004システム構成図 [画像のクリックで拡大表示] |

詳細な論理設計に入る前に,再度,4004CPUの詳細な機能ブロック図を書き上げ,機能モジュール間のインタフェースを明確化した。チップサイズと性能に非常に大きな影響を与える作業だ。納得いくまで,何度も繰り返した。そのためには,論理設計ばかりでなく,次の設計段階である回路設計とレイアウト設計にも精通しなければいけないことを実感した。

1つのトランジスタも無駄にしないように,各機能モジュールの論理設計を開始した。最初に,総トランジスタ数を算出する必要もあり,論理設計は簡単だが多くのトランジスタを必要とする汎用レジスタ,アドレススタック,命令レジスタ,タイミング,コマンド制御,システムバスなどのモジュールの論理設計を行った。

汎用レジスタ・モジュールを,汎用レジスタ本体,レジスタ番号を指定するアドレスデコーダ,データの読み書き回路,リフレッシュ用カウンタで構築した。リフレッシュ用カウンタとは,DRAMメモリーに格納したすべてのデータを一定間隔で逐次的にリフレッシュする時のリフレッシュするレジスタを指定するカウンタである。アドレススタック・モジュールを,スタック本体,アドレスデコーダ,データの読み書き回路,アドレス更新回路,リフレッシュ用カウンタで構築した。命令レジスタには8ビットのドライバ付スタティック型フリップフロップを使用した。

タイミング・モジュールでは,アドレスや命令やデータを4ビット単位で処理するために,アドレス送出時用タイミングとしてA1とA2とA3を割り当て,命令読み込み時用タイミングとしてM1とM2を割り当て,命令実行時用タイミングとしてX1とX2とX3を割り当てた。命令の1サイクルが8つの固定したタイミングになるように論理を構成した。トランジスタ数を減少させるために,命令長が2バイトの場合には,2サイクルを使う論理を採用した。また,外部のROMとRAMでも命令を解読し実行するために,サイクルを開始する1つの前のタイミング情報をSYNC信号として外部に送出した。このことにより,外部のROMとRAMを4004CPUと同期をとって制御することが可能となった。

コマンド制御モジュールに,プログラムで使用するROMとRAMのチップを指定するコマンドレジスタを設けた。4ビット時分割双方向システムバスとのインタフェースであるシステムバス・モジュールを,4ビットのドライバ付出力用フリップフロップと4ビットのドライバ付入力用フリップフロップなどで構築した。

最後に,テスト時間の短縮のためにアキュムレータとキャリーの内容をシステムバスの空いている時間に自動的に送出させた。

出来上がった論理を何度も見直したが,トランジスタの削減の余地は全くなかった。使用したトランジスタ数は,汎用レジスタ・モジュールで402,アドレススタック・モジュールで374,命令レジスタで72,タイミング・モジュールで99,制御用コマンド・モジュールで100,システムバス・モジュールで92,合計1,139となった。残りのトランジスタ数は861で,2入力論理ゲートに換算すると僅か287ゲートとなった。残った論理は,アキュムレータ,キャリー,ローテート回路,10進補正回路などを含む4ビットの主演算回路モジュールと,命令デコーダを含む命令実行制御モジュールであった。この時点で,2,000個のトランジスタという目標は達成不可能となった。

いよいよ,プロセッサ開発の山場に近づきつつあった。残った両モジュールには,設計の難しさと楽しさが同居している。他人にはやらせたくないモジュールである。主演算回路モジュールに関しては,納得するまで,自分の考え方を埋め込むようにして,配置配線も考え,何枚ものスケッチ的な図を描き,そして考え続けた。5回以上繰り返したと記憶している。主演算回路モジュールに使用したトランジスタ数は329個であった。

主演算回路,コマンド制御,汎用レジスタ,アドレススタック,システムバスなどのモジュールに対する命令実行の制御には,命令を解読する命令デコーダと命令をグループ化する命令エンコーダなどの出力とタイミング信号(A1,A2,A3,M1,M2,X1,X2,X3)とのAND論理で構成する組み合わせ論理方式を使用した。

命令実行制御モジュールのランダム論理量を少なくするために,論理を組み足していく論理構築方法と,ある特定の論理で否定する論理構築方法と,条件なしの論理で組む論理構築方法などを組み合わせて使用した。拡散層とポリシリコン層を直接結合させるBuried Contactを使用したため,すべての組み合わせ論理回路をタイミング信号のメタル層の下で形成することが可能となり,チップサイズの減少が図られた。Buried Contactはフェアチャイルド社で1968年にファジンによって発明された結合方法である。

主演算回路とコマンド制御の制御には,32項数のProgrammable Logic Array(命令デコーダに26項,命令エンコーダに6項,使用トランジスタ数は158)と命令実行制御の組み合わせ論理に202個のトランジスタ(約67ゲ-ト)を使用した。また,汎用レジスタとアドレススタックとシステムバスの制御には,22項数のPLA(命令デコーダに22項,使用トランジスタ数は111)と命令実行制御の組み合わせ論理に298個のトランジスタ(約99ゲ-ト)を使用した。命令デコーダと命令エンコーダを含む命令実行制御に使用したトランジスタ数は769であった。

最終的に,4004CPUの総トランジスタ数は2,237となった。後年,4004CPUのトランジスタ数を,ホフは2,108,ファジンは2,300(PLAで実装していないトラジスタも含んでいる)と言っているが,実際のトランジスタ数は2,237であった。

完成した論理を回路設計やレイアウト設計に使えるように,トランジスタのサイズが入っていない論理回路図面の作成に着手した。まず,A2サイズの紙を3枚用意した。各モジュールとのインタフェースを考慮しつつ,左側の1枚に主演算回路モジュールとコマンド制御モジュールとタイミング・モジュールとシステムバス・モジュールを,右側の1枚に汎用レジスタ・モジュールとアドレススタック・モジュールを,中央の1枚に命令レジスタと命令デコーダ/エンコーダを含む命令実行制御モジュールを描いた。

| 機能 | トランジスタ数 |

|---|---|

| 合計トランジスタ数 | 2,237 |

| 命令レジスタ | 72 |

| 命令デコーダと命令実行制御モジュール | 769 |

| 主演算回路モジュール | 329 |

| 汎用レジスタ・モジュール | 402 |

| アドレススタック・モジュール | 374 |

| タイミング・モジュール | 99 |

| コマンドレジスタ・モジュール | 100 |

| システムバス・モジュール | 92 |

|