開発の正式契約が1970年3月に結ばれ,4月7日に私一人でインテルを訪問した。正式契約では2人の論理回路設計者が雇われる計画だった。したがって,今度の訪問目的はインテルが設計している論理回路図の確認であった。かなりの進ちょくを期待して,インテルを訪問した。

ホフは新しい回路設計技術者であるファジン(Federico Faggin)というイタリア人技術者を紹介して,「後は彼が担当するから」と言い残して,休暇を取ってしまった。拍子抜けしたばかりでなく,何か不吉な予感が頭を横切り,あっという間に期待が不安に変わった。

ファジンに聞くと,「私は2日前にフェアチャイルドからインテルに入社したばかりで何も知らない」と言う。少し強い口調で,「設計図を見せてくれ」と問うと,「何もない」と言う。本当に1枚の図面もなかった。設計は全く進行しておらず,仕事の引き継ぎに関してもメイザーからの簡単な説明以外は全くなされていなかった。メイザーからの説明の翌日に私が訪問したとのことである。

契約書では2人の技術者を雇うことになっていたが,4ビットのコンピュータということで,誰にも興味を持たれず,論理回路設計者を雇うことができなかったらしい。正式な契約が遅れたせいかもしれないが,なんて不誠実な会社だと思い,“激怒しない客がいたら見たいものだ”ぐらい,かなり強い口調で抗議した。今でも,「嶋が激怒した」と言われ続けている。渡米前に知らせてくれれば,なんとしてでも準備して渡米したのにと,残念で仕方がなかった。

3月20日にノイス宛に送った手紙の内容は誰も知らない振りをしていた。ファジンは知らなかっただろう。

|

| 図1●ファジン博士と私(米国でのマイクロプロセッサ・フォーラムにて) [画像のクリックで拡大表示] |

私のインテル訪問に少し遅れて,ビジコンの顧問弁護士が到着した。インテルの技術部長レス・バデーズに1970年2月16日付けの開発スケジュール表を提出してもらった。しかし,その計画はビジコンの生産計画に比較して大幅な遅れがあった。プロセッサに4004,ROMに4001,RAMに4002,SRに4003の製品番号が正式に与えられていた。

1970年2月20日に作成した開発スケジュール表をみて,また驚いた。機能仕様書決定後の論理と回路とレイアウトの設計期間は,プロセッサで8週間(設計開始:6月28日),RAMで7週間(5月17日),ROMで4週間(5月3日),出力ポートSR(7月5日))で6週間(5月31日),合計設計期間は4カ月という計画となっていた。さらに,それぞれのレイアウト図面からマスターマスクカットに4週間,マスク作成に2週間,プロセスに1.5週間,デバッグと次のステップへのレイアウト変更とマスクなど作成に4週間となっていた。論理と回路の設計期間はほとんど無いも同然の計画案だった。

人員計画としては,技術者が2名,マスク設計者が3名と計画されていた。4004CPU開発のため,2番目の技術者を6月に採用する予定となっていた。当時のインテルには論理設計の経験者がいなかったため,論理や回路などの設計期間は非常に低めに見積もられた。論理と回路は2週間ぐらいで設計できるだろうと思っていたらしい。この傾向は8085マイクロプロセッサの開発直前まで続いた。技術者1人とマスク設計者2人では実現不可能な計画案であった。プロジェクトの最後の頃に,テクニシャンとマスク設計者が1人ずつ加わったが,スケジュール表を見せられたファジンは何を思っただろうか。

このままでは,プロジェクトは失敗すると判断した。顧問弁護士と相談し,正式契約締結日または仕様書の受理日から半年以内の試作品出荷,ブレッドボードを作成して4004システムの機能検証を早期に行うためのRAMとSRの開発スケジュール前倒し,CADを使った論理シミュレーションのインテルによる実施,論理設計と論理シミュレーションとテストプログラム作成に関して嶋の全面的な協力,などのビジコンの要求をインテルに伝えた。ホフの休暇明けに,再度,詳細なスケジュールを話すことになった。

この後,インテル社内はフリーパスで何処へでも行くことができた。

ファジンに抗議しても仕事が進まないので,私がファジンに4004CPUと4004ファミリーLSIの機能仕様書と製品設計計画案を説明した。4001ROMと4002RAMと4003SR(シフトレジスタ)に関しては,設計案に詳細なブロック図とタイミング図と論理表を加えた簡単な書類を大至急書き上げた。

ホフの休暇明けに,仕事の分担を決めた。私の担当は,4004CPUの論理設計,論理シミュレーション,レイアウトチェック,テストプログラム作成となった。ファジンの担当はRAMとROMとSRのすべての設計と4004の回路設計とレイアウト設計となった。ホフの担当は論理シミュレータ用CAD作成となった。東京のビジコンでは,私が作成した論理図に基づいてTTL回路などを使って4004CPUをエミュレートするブレッドボードを作り,私の論理シミュレーションと平行して論理の検証を行うことを決めた。

4月以来,私はファジンと同じ部屋で,2人で月曜日から土曜日まで毎日12時間ほど仕事中毒患者のように働いた。私がプロセッサと論理設計を,ファジンが回路設計と回路シミュレーションとレイアウトを,お互いに教えあった。レイアウトの細かいことは2人のマスク設計者が教えてくれた。素晴らしいチームが出来上がりつつあった。アメリカの会社と日本の会社の大きな違いの一つに仕事の密度がある。アメリカ流に力を入れ,集中して朝8時から夕方5時まで働くと,肉体も精神もクタクタになってしまう。仕事が夕方で一段落しても,ファジンや日本との打ち合わせなどがあり,体がいくつあっても足りなかった。自分でも驚くほど仕事への体力が付いた。

4004シリーズLSIを設計するにあたって,回路設計をいかに短期間に完了させるかがスケジュールの最大の鍵となった。当時のインテルには社内用コンピュータがなく,回路シミュレーションには電話回線を使って外部の計算センターを利用していた。ただし,外部の計算センターとの通信を行うテレタイプ社製ターミナルのプリント出力性能は1秒間に10文字と非常に悪く,大きな回路シミュレーションを行うにはかなりの時間が掛かってしまう。大規模なランダム論理回路網の回路シミュレーションは,時間的にも金銭的にも事実上不可能であった。

ファジンは回路設計の手法を考案した。コンピュータを使って基本的回路の回路シミュレーションを行い,その結果を使って回路設計マニュアルを作成した。基本的回路を組み合わせて複雑な回路を構築し,回路設計マニュアルを使って遅延時間を見積もり,最適化後に,回路シミュレータで遅延時間を確認し,回路設計の高効率化を図った。

プロジェクトには男性1人と女性1人の優秀なマスク設計者が参加した。しかし,シリコンゲートMOSテクノロジーを使ったレイアウトの経験者が1人しかいなかった。このため,ファジンがレイアウト設計に関してのレイアウト・ガイドラインや個々の基本的なレイアウトプランを立てた。

ファジンの仕事振りを身近に見ていたので,後年,これらの設計手法は私の財産になり,8080やZ80の開発において大いに役に立った。ROMの設計にあたっては,アドレスラインの配線にポリシリコンが使われるのだが,配線長が長くなると,配線抵抗が大きくなり速度が低下する恐れがあった。私の提案でROMを2つのブロックに分割し,アドレスライン長を半分にして高速性を維持する設計を行った。

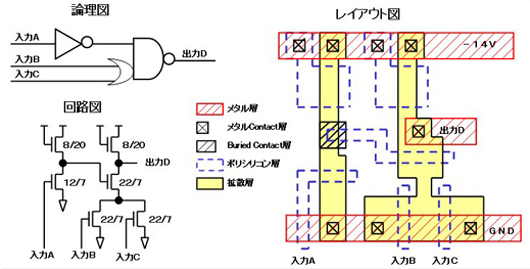

下図に,論理図と回路図とレイアウトの例を示す。このレイアウト手法も私の財産となった。

|

| 図2●論理図と回路図とレイアウトの例(仮想のデザインルールを使用) [画像のクリックで拡大表示] |

汎用レジスタと,プログラムカウンタを含むアドレススタックの両方を,6個のトランジスタを使ったSRAMセルではなく,当時開発中の1KビットDRAMメモリー(1103)に採用した3個のトランジスタを使ったDRAMセルを使うことが前回の訪問時に計画されていた。幸いなことに,3トラジスタDRAMセルを使用すると,データの読み出し回路と書き込み回路が別々に用意されている。

4004シリーズではオーバーラップしない2相クロックを使うために,アドレススタックの読み書き回路にアドレス更新回路を組み込み,1相目のクロックでアドレスまたはデータを読み出し,2相目のクロックで更新したアドレスまたはリフレッシュしたアドレスやデータを書き戻す論理を考えた。

論理設計を進めていくと,また難題が降りかかってきた(次回に続く)。