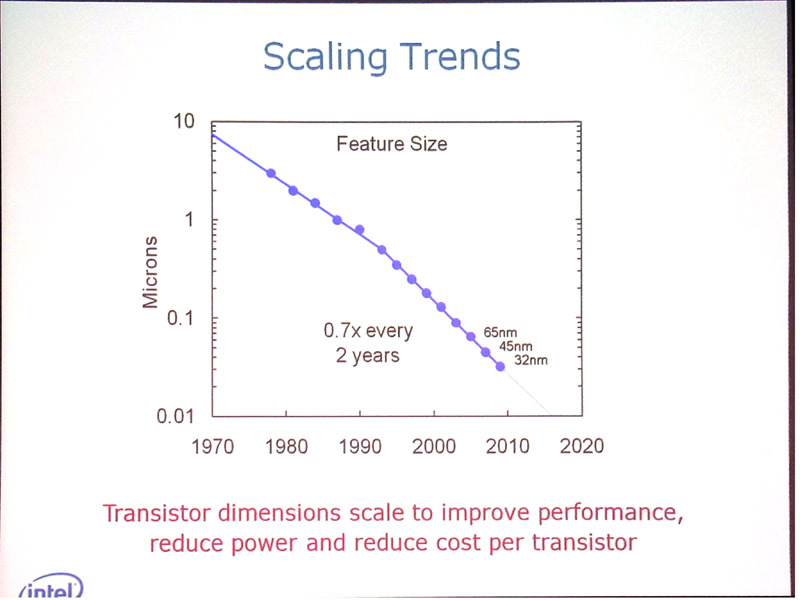

2010年4月13~14日に中国・北京市で開催されている「Intel Developer Forum(IDF)」において、Intelで製造プロセス技術の研究開発を担当するLogic Technology Developmentのシニアフェローであるマーク・ボーア氏が日本の報道関係者との取材に応じた。ボーア氏は製造プロセスの進化が消費電力の低減と性能の向上を果たしてきたと説明。微細化技術の進展は順調に継続しており、ムーアの法則による性能向上のカーブがまだ続いていることを示した。

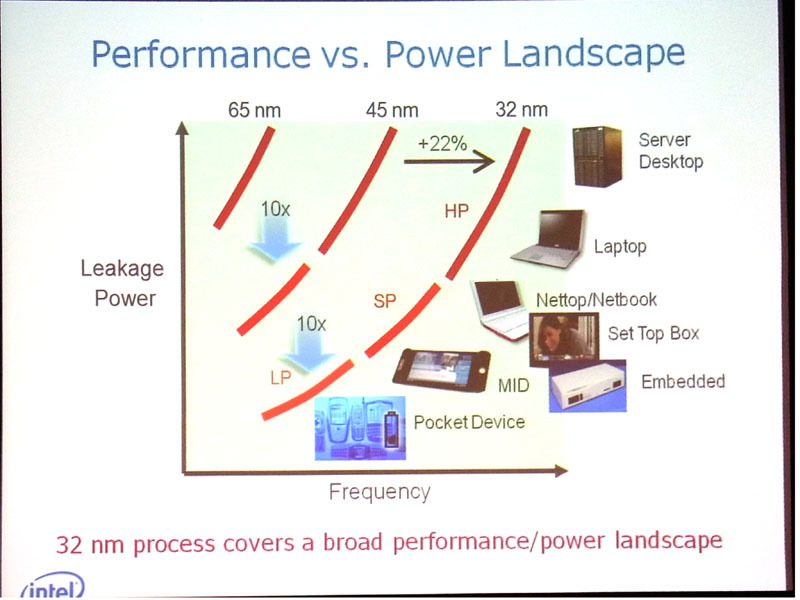

ただしその製造プロセスがもたらすメリットを性能だけに注ぎこむのではなく、消費電力の低減にも盛り込むようになってきた。これが45nm世代から始めた製造プロセスの「プロファイル」に相当するものである。45nm世代からCPU向けとは異なり、消費電力を抑えたSoC向けのプロセスを開発するようになった。これが32nm世代では「LP」として使われている。SoC向けのプロセスでは、ゲートにHigh-Kだけでなくシリコン酸化物の層も重ねることによって、リーク電流をさらに抑えている。また高速動作では電流量を稼ぐために配線に使う金属の幅を広く取る必要があるが、SoC向けではチップ面積を減らすために極力幅を狭めるといった違いがある。「消費電力に対する要求が高まってきたことにより、製造プロセスでも工夫が必要になってきた」(ボーア氏)。

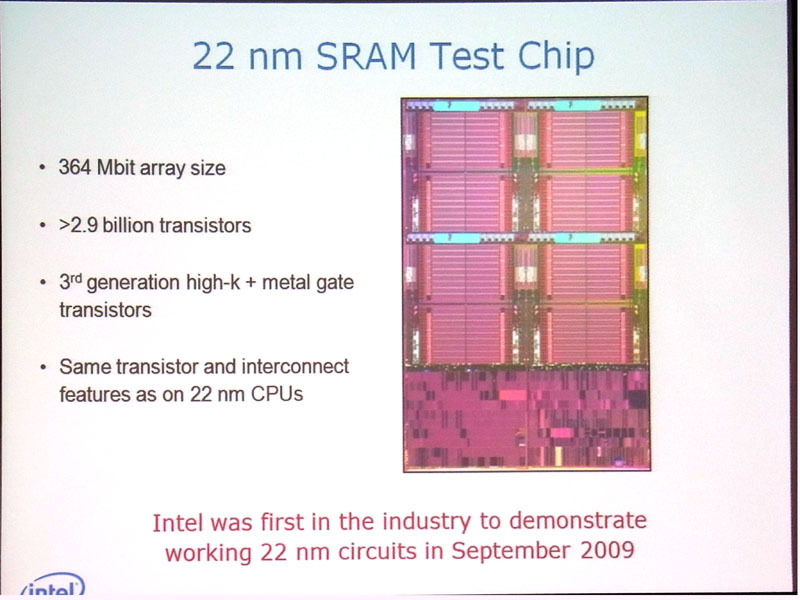

次の製造プロセスは22nmだが、これは現状のHigh-K金属ゲートの技術の延長線で実現可能である。既にIntelは2009年11月に、22nmプロセスで製造したSRAMのワーキングサンプルを開発済みである。2011年の生産開始に向け、順調に開発が進んでいるという。

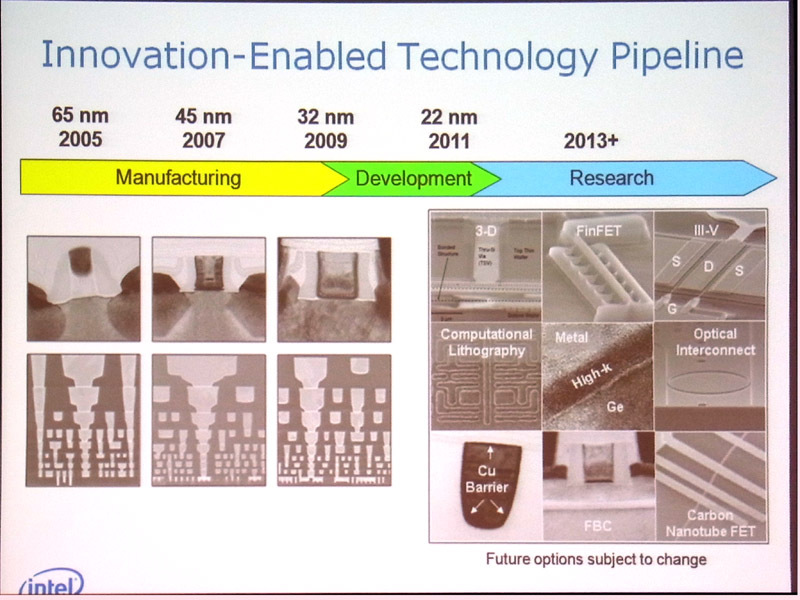

課題はむしろその先にある。製造プロセスの短縮化により、一つひとつのトランジスターに割り当てられる面積が狭くなる。トランジスターを構成するのに必要なシリコンの量を確保できなくなる可能性が出てくる。「おそらく15nm世代では、3次元構造のトランジスターやマルチゲートのトランジスターなど、新しい技術が必要になってくるだろう。そのための研究開発を進めている。どれか特定の技術というわけではなく、さまざまな候補を検討している段階だ」(ボーア氏)。