どうすれば消費電力を抑えたルーターを設計できるのでしょうか。LSIのテクノロジや,給電方法,基板材質など一般的に多くのアプローチがあります。ただ,これら一般的な省エネ対策とは別に,ルーターの構造から取り組むべき対策があります。

ルーターは,その処理性能によって構造が異なります。特に,キャリアクラスのルーターの中でもスイッチング容量が80Gビット/秒を境界に,それより容量の小さいルーター(ミッドレンジ・ルーター)と大きいルーター(ハイエンド・ルーター)では,基本的な構造が大きく異なります。10Gビット・イーサネット(以下,10GbEと略します)だと,装備するポート数が4個までと5個以上で構造が変わるわけです(全2重なのでスイッチング容量は回線速度の合計の倍になります)。これは,80Gビット/秒というスイッチング容量に技術的な壁があるからです。この構造の違いが,消費電力に大きく影響しているのです。ここに着目して,改善策を考えました。

ちょっと詳しい話になりますが,ルーターのスイッチング容量と構造および消費電力の関係について見ていくことにします。

ボトルネックとなるメモリーの帯域

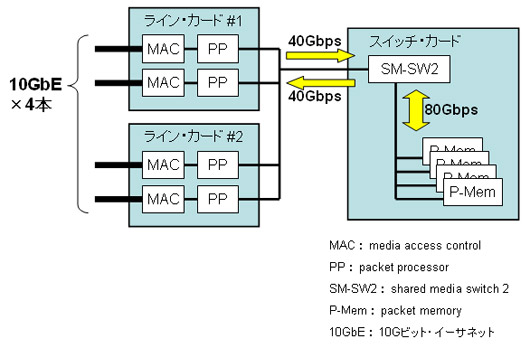

最初に,10GbEを4ポート収容するルーター(以下ミッドレンジ・ルーターと呼びます)の内部構造がら見ていきましょう(図2)。10GbEを2本収容するライン・カードを2枚実装し,装置全体で10GbEを4本収容します。これで,80Gビット/秒のスイッチング容量を実現しようというわけです。

| |

| 図2●ミッドレンジ・ルーターの構造 80Gビット/秒(10Gビット・イーサネット4本)までのスイッチング容量を実現する。 |

ライン・カードには,10GbEのイーサネット・フレームを処理をするMAC(media access control)と,10Gビット/秒の性能でパケットを解析し,あて先を検索したりするPP(packet processor)の2種類のLSIが搭載されます。

そのライン・カードを取りまとめるのがスイッチ・カードです。スイッチ・カードには,データを交換処理するための共有メモリー・スイッチ(shared memory switch 2:SM-SW2)とパケット・メモリー(packet memory:P-Mem)の2種類のLSIが搭載されています。SM-SW2は,複数のPMとの間でデータをやりとりすることでパケットの交換処理を実行します。

実際の処理の流れは,(1)ライン・カードに送られてきたパケットはラインカードのMACとPPを経由してスイッチ・カードに送られ,(2)スイッチ・カードのP-Memにいったん格納され,(3)SM-SW2が格納したパケットのあて先を探し,(4)P-Memに格納されたパケットを読み出してあて先のライン・カードへ送り出し,(5)ライン・カードでPPとMACを経由してポートへ出力される――という格好になります。

この流れの中で速度的なボトルネックになるのが,(2)と(4)の部分,つまりSM-SW2とP-Memのやりとりになります。実際に,複数のメモリーLSIで実現されるP-Memの帯域をここで具体的に算出してみましょう。

現在サーバーなどで使われる標準的なメモリーで高性能なものは「DDR2-667」です。これは,32ビットのデータ幅を転送レート667Mビット/秒で処理できるものです。このメモリーを並列で処理させて帯域を拡張するのですが,SM-SW2のピンの数を現実的な範囲に抑えつつ,並列で安定動作させることを考えると,並列で使用できるDDR2-667の技術的な上限は4個になります。

32ビット幅のデータを677Mビット/秒で処理できるメモリーを4個並列で動かすので,この部分の転送速度は32(ビット)×677M(ビット/秒)×4(個)で85,376Mビット/秒となります。アドレス情報の転送やリフレッシュなど,その他の制御系の処理を差し引くと,約80Gビット/秒の帯域を利用できる計算です。さらに,データ受信時のWrite動作とデータ送信時のRead動作で使い分けるとして,40Gビット/秒の受信用と40Gビット/秒の送信用の帯域が確保できます。

つまり,図2の構造ではこれ以上ライン・カードを増設できないということになります。10GbEのポートをさらに増やして処理性能を上げるには,別の構造にしなければならないのです。