ここまで,キャリアクラス・ルーターの構造とその違いによる消費電力の差について見てきました。スイッチング容量が80Gビット/秒を境にして,それより小容量のミッドレンジ・ルーターに比べて,大容量のハイエンド・ルーターは,1Gビット/秒のスイッチング容量あたりの消費電力が30%程度大きく,非効率的です。

では,こうしたルーターの消費電力を効率化するにはどうすればいいのでしょうか。そこで私たちは,メモリー帯域のボトルネックと,クロスバ・スイッチの効率に着目して,省エネ化の対策を考え,実現する方向でルーターの開発を進めています。ここでは,その中から二つの方策を紹介しましょう。

方策1:メモリー帯域のボトルネック解消で容量拡大

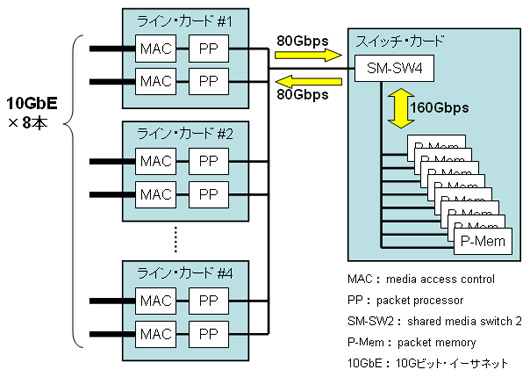

ここまで,キャリアクラス・ルーターのボトルネックは,共有メモリー・スイッチ(SM-SW)とパケット・メモリー(P-Mem)の間の帯域の上限が80Gビット/秒だと説明してきました。であれば,このボトルネックとなる部分の帯域をなんとか拡張すれば,消費電力を抑えたミッドレンジ・ルーターの構造のまま,全体のスイッチング容量を向上できるはずです。

その一つの手段が,現状のように標準的なDDR2メモリーを4個使うのではなく,より多数のメモリーを使えるようにするというものです。SM-SWに接続するDDR2メモリーが4個までに制限される大きな理由が,SM-SWのピン数です。接続するメモリーが多くなればなるほど帯域は拡張できますが,接続するためのピンの数が膨大になり,SM-SWを安定して動作させることが難しくなります。

つまり,SM-SWとP-Memの間の帯域を向上させるには,ピン数を増やさずにより多くのメモリーを接続することが必要になります。SM-SWとメモリーの間でやりとりする多数の信号を高速化して集約するといった工夫を加えれば,接続できるP-Memの数は増えます。P-Memの数が6個,8個と使えるようになれば,ミッドレンジ・ルーターのスイッチング容量の上限を120Gビット/秒や160Gビット/秒に向上できるのです(図4)。

|

| 図4●改良版ミッドレンジ・ルーターの構造 160Gビット/秒(10Gビット・イーサネット8本)まで容量を向上する |

信号部分の高速化ではなく,RLDRAM(reduced latency DRAM)やFCRAM(fast cycle RAM)などネットワークに特化したメモリーを使うことや,さらに特殊なメモリーを独自開発することで,帯域を向上したり消費電力を抑えるといった可能性もあります。