さて,いよいよ今回から実験を開始します。まずは,実験のターゲットと,JTAGエミュレータの接続について説明します。

実験には,米国で普及しているX社製のブロードバンド・ルーターを利用しました。このルーターには,前回解説した第一の条件である脆弱性が存在するためです。ルーターの設定などで利用される内蔵Webサーバーに,スタック・ベースのバッファ・オーバーフロー脆弱性があります。

リモートから攻撃可能ですが,デフォルトではLAN側からしか攻撃できませんので可,脆弱性の性質としては,それほど深刻なものではありません。なお,この脆弱性は最新のファームウエアでは修正されています。

また,CPUにはSamsung社製のS3C4510Bが利用されていることが分かっているので,CPUに関する詳細情報を入手できます。

JTAGポートの実装

JTAGをサポートしているCPUには,以下に示す5つのテスト・アクセス・ポート(TAP)ピンがあります。

・TCK:TAPコントローラの動作を同期化するクロック信号

・TMS:内部ステートマシン・モードの選択信号

・TDI:データ入力

・TDO:データ出力

・TRST:非同期リセット(オプション)

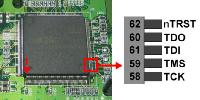

これらのピンにケーブルを接続し,入手したCPUのマニュアルに従ってJTAGポートを作成します。以下に,S3C4510BのTAPピン(図4)とJTAGポートの回路図(図5)を示します。

図4. S3C4510B TAPピン [画像のクリックで拡大表示] |

図5. S3C4510B JTAGポートの回路図 [画像のクリックで拡大表示] |

ケーブルは,CPUのTAPピンにハンダ付けして接続します。CPUのピンのピッチは非常に狭いので,かなり熟練したハンダ付けの技術が必要です(慣れていないとすぐにブリッジしてしまいます)。ただ,TAPピンは通常はシステムの動作に影響しませんので,これらを基盤からはがして広げ,ハンダ付けしても問題ありません。細めのぬい針をピンとピンの間に入れ,上に押し上げると比較的簡単にはがすことができます。こうすれば,容易にハンダ付けできます。

図6. ピンを基盤からはがす [画像のクリックで拡大表示] |

図7. JTAGポートの実装 [画像のクリックで拡大表示] |

JTAGのポートやパターンが基盤に残っている場合もあります(図8)。この場合にはハンダ付けをしなくて,簡単にJTAGポートを作成できます。実際,非常に多くの組み込み機器で,このような“開発の名残り”を目にします。ひと目でJTAGポートと分かるようなパターンを基盤に残すのは避けるべきでしょう。

図8. TAGパターンの例 [画像のクリックで拡大表示] |

BGA(Ball Grid Array)のように,ピンの見えないパッケージがCPUに採用されている場合には,TAPピンに直接ケーブルを接続できません。この場合,攻撃者は基盤上からTAPピンの先を探す必要があります。加えて,基板上にバラバラに配置されているとなると,これは少々骨が折れる作業になると思います。このように,攻撃者にTAPピンを触せない工夫を施すことで,攻撃のハードルを高めることができます。(第7回へ続く)

|

「Security Tech」は,米eEye Digital SecurityのSenior Software Engineerである鵜飼裕司氏による技術コラムです。鵜飼氏はMicrosoft製品のセキュリティ脆弱性(セキュリティ・ホール)を多数発見していることでも知られるセキュリティの専門家です。

本コラムでは,あるテーマについて数回にわたって技術解説記事を執筆していただきます。1回目のテーマは,「組み込みシステムのセキュリティ」。全8回にわたって,組み込みシステムにおけるセキュリティ脆弱性の脅威の実際と,開発サイドに求められる組み込み機器独特の防衛策について解説していただきます。 なお,鵜飼氏には「ITpro Watcher」も執筆していただいております。こちらのほうも,併せてお読みいただければ幸いです。(編集部より) |