![]()

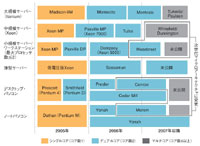

核となるのは,消費電力当たりの性能を高める次世代マイクロアーキテクチャへの転換。2006年後半にデスクトップ・パソコンとノートパソコン向けに次世代マイクロアーキテクチャ採用のデュアルコアCPUを出荷(図1[拡大表示])。やや遅れて,サーバー向けにも同じコアを利用したデュアルコアおよび4コア以上のマルチコア製品を投入する予定だ。

次世代マイクロアーキテクチャに関する基調講演やセッション以外は,2005年春のIDFで打ち出した「プラットフォーム重視」の戦略に沿ったもの。CPU以外の製品を含めたプラットフォームの優位性を説く内容が中心で,目新しさは少ない。今後10年を見越した将来構想についても,並列プログラミングの負担を軽減する「Platform 2015」と呼ぶ構想に触れたが,すでに提言済みで新規性に欠けていた。

その中で目を引いたのは,2日目の基調講演で発表した新ブランド「Viiv」と,3日目の基調講演で披露したSoC(System on a Chip)の試作チップ。前者はIntelプラットフォームの採用を条件に販売促進用のロゴを付与するマーケティング手法。後者はCPUにメモリー・コントローラだけでなく電源制御用のCMOSレギュレータを混載したものだ。

次世代プロセッサの輪郭を披露

次世代マイクロアーキテクチャは,現在デスクトップ向けのPentium 4やサーバー向けのXeonで使われているマイクロアーキテクチャと,ノートパソコン向けプロセッサのPentium Mを融合させたもの(写真1[拡大表示])。モバイル向けもサーバ ー向けも共通のアーキテクチャとなる。新アーキテクチャを採用したCPUは,ノートパソコン向けが「Merom(開発コード名)」,デスクトップ向けが「Conroe(同)」,サーバー向けが「Woodcrest(同)」。それぞれ2006年後半に登場する予定だ。

Merom/Conroe/Woodcrestの具体像は明らかにしなかったが,熱設計の目安となる熱設計電力(TDP)は,ノートパソコン向けで5W,デスクトップ向けで65W,サーバー向けで80WのTDPを実現する。現在の低電圧版Pentium Mが10W前後,Pentium 4が100W前後であるのに比べると,ほぼ半減する。

実現のために盛り込んだ工夫のうち,現時点で明らかにしたのは大きく四つ。(1)Pentium 4系列とPentium M系列の「良いとこ取り」,(2)電力効率を高める工夫,(3)コア間で共有する2次キャッシュ利用の効率化,(4)メモリー・アクセスに割く時間の短縮である。いずれも概要にとどまり,詳細はほとんど明らかではない。例えば(3)については,1次キャッシュ間でデータを直接転送する機能の追加と,2次キャッシュ帯域の拡大。(4)はプリフェッチの改良と,実行前に命令の依存関係を明らかにする機構によって実現するという程度である。

比較的明確なのは(1)。Pentium 4系列からはプロセッサ・バス(動作周波数は不明)と仮想化技術/64ビット対応などの拡張機能を,Pentium M系列からは同時実行可能な命令数を重視した設計思想を,それぞれ引き継ぐ。

具体的には,1サイクルで同時に実行可能な命令を従来の3個から4個に増やしつつ,動作周波数を左右する命令の読み込みから実行までのステップ数(パイプライン段数)を現行Pentium 4の31に比べて約半分の14に減らした。

一般にCPUは回路を単純にしてパイプラインの段数を増やし動作周波数を高めている。半面,パイプラインの段数が多いほど,命令やデータに依存関係があった場合に命令の読み込みから実行をまでをやり直すサイクルが増える。この副作用を低減するため,Pentium 4系のCPUは同時に二つのスレッドの命令を読み込んで実行するHyper-Threading機構(HT)を組み込んだ。

しかしパイプラインの段数が半減した次世代アーキテクチャでは必要性の薄い機構となる。そのため,最初の実装ではHTを搭載しない。ただし「将来的に実装する可能性はある」(Pat Gelsinger上級副社長)。スレッドがふんだんにあるサーバー・アプリケーションではそれでも効果があるからだ。

(2)の電力効率の工夫とは,「スリープ・トランジスタ」の実装などの改良と見られる。電源を遮断するスイッチに相当するトランジスタを追加して,使われていない回路の消費電力を減らす。

2次キャッシュの分割管理で省電力化

2006年第1四半期の出荷を予定するPentium M後継のデュアルコアCPU「Yonah(開発コード名)」については具体的な実装を公開した。ここから,Merom/Conroe/Woodcrestの省電力化の工夫の一端が見えてくる。消費電力当たりの性能を高める手法はYonahが土台となるからだ。

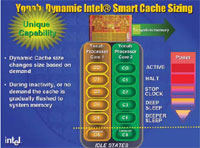

今回のIDFで明らかにしたのは省電力機構の詳細だ。2次キャッシュを八つのブロックに分割し,個別に電源を管理して消費電力の削減を図る(写真2[拡大表示])。

一般にメモリーへのアクセスには局所性があり,アプリケーションによっては2次キャッシュの容量差が性能にさして影響しない場合がある。そこで2次キャッシュの容量を動的に変える「Intel Smart Cache Sizing」と呼ぶ機構を用意。アクセスのないブロックに保持するデータをメモリーに退避させたうえで電源を遮断する。2次キャッシュ全体へのアクセスがない場合は,2次キャッシュの内容すべてをメモリーに書き出して消費電力を下げる。

国内ではインパクトに欠けるViiv

「ViivはCentrinoに続く第2のブランド」(コンシューマ向け製品を担当するDigital Home事業部のDonald J. MacDonald副社長)。CentrinoがPentium M/チップセット/無線LANモジュールの採用を条件としたのと同様に,同社製のマルチコアCPUやチップセット,米Microsoft社のメディア配信サーバー向けOS「Windows XP Media Center Edition(MCE)」の採用などを条件にViivロゴを付与する(写真3[拡大表示])。各種コンテンツのフォーマットを自動変換する機能を仕様に含むなど,マルチコアCPU普及の推進策でもある。2006年の第1四半期の製品出荷を見込んでいる。

もっとも日本国内では,テレビ録画やDVD再生を売りにするのは当たり前。高画質化で競うのが今のトレンドだ。Viivブランドの推進は,日本以外の海外メーカー向けの施策という印象だ。

SoCのPentium Mを初公開

最終日の基調講演では,Corporate Technology Group Director兼Senior FellowのJustin R. Rattner氏がx86互換CPUをベースにした同社として初めてのSoCチップを披露した。Pentium M 768(1.4GHz動作)とメモリー・コントローラ(855GMのノースブリッジ),およびCMOSを使ったレギュレータを1パッケージに混載した(写真4[拡大表示])。

CPUとメモリー・コントローラの混載や集積は珍しいことではない。注目すべきはCMOSレギュレータ。「プロセッサ外にある電圧制御用のレギュレータは動作速度が遅い」(Rattner氏)。CMOSレギュレータの混載で電圧の上げ下げにかかる時間を短縮。外部レギュレータによる制御に比べて,30~35%消費電力を削減した。これにより20~40分バッテリ駆動時間を延長できたという。製品化の時期は未定である。

電子カルテの標準化に本腰Intelは2005年1月に実施した機構改革で,医療事業を担当するDigital Health事業部を新設した。今回のIDFで,Digital Health事業部を率いるLouis J. Burns副社長が,医療機器分野への取り組みを初めて大々的に公表した。 Burns副社長が指摘したのは,医療機関における情報化の遅れ。「医療機関の情報システムは民間企業に比べると10年遅れている」(同氏)。コンピュータによる自動化で医療機器と人手による管理を排除し,医療過誤低減とコスト削減を狙う。

取り組みの実例としてデモしたのは,在宅医療用の携帯情報機器(写真[拡大表示])。患者役のデモ員に無線ICタグを内蔵する識別用リストバンドを装着し,脈拍や血圧,体温,酸素飽和度など取得した。さらにネットワークを通じて患者の情報を転送して見せた。「患者の情報を書類に手書きしなくても送信できる。医師の不在時でも,医師が持つ情報端末に正確なデータを瞬時に届けられれば,医師はそのデータを閲覧して患者やその家族に指示を出せる」(Burns氏)。 また,運動機能をテストするA5型ノートパソコン大の専用端末も披露。マッチ棒程度のピンを別の穴に差し替える「ペグ移動」テストや発話の揺れなどの情報を取得して,病状の把握に役立てられるという。 医療データの共有で過誤を減らすもっとも医療用の携帯情報機器自体は珍しくない。本腰を入れるのは,データ形式の標準化による医療データの相互利用だという。「データ形式の標準化ができていないために,200万件の薬の副作用情報,10万件の医療過誤の情報を医療機関で共有できていない。情報共有ですべて解決できるわけではないが,予防に効果がある」(Burns氏)という考えを示した。Burns氏の家族が受けた治療の際に,「交代した医師は19年の病歴を3分で理解しなくてはならず,看護師による記録が間違っていることもあった」という自らの体験を明らかにする一幕もあった。 基調講演終了後の報道陣向けの質疑応答では,(1)標準化の実現可能性,(2)個人情報の保護,(3)ビジネスモデル,の3点が焦点となった。 Burns氏は(1)について,「世界の官公庁にIntelのシステムの導入を呼びかけていく」とし,デファクト・スタンダードからの標準化を目指す考えを示した。(2)に関しては,あくまでも可搬性のある機器に情報を集積することで「情報が個人について回るようにする」としたうえで,「同じような書類を何度も書く必要がなくなる」という患者のメリットを強調した。(3)は「まずは標準化への取り組みを成就させるのが先決。これにより民間企業の情報システムに比べると10年遅れている状況をばん回できる」と言及を避けた。 |